- 您现在的位置:买卖IC网 > Sheet目录1997 > ICS8421002AGILF (IDT, Integrated Device Technology Inc)IC FREQ SYNTHESIZER 20-TSSOP

FEMTOCLOCKS CRYSTAL-TO-HSTL

FREQUENCY SYNTHESIZER

ICS8421002I

IDT / ICS HSTL FREQUENCY SYNTHESIZER

1

ICS8421002I REV B

MARCH 02, 2009

GENERAL DESCRIPTION

The ICS8421002I is a 2 output HSTL Synthesizer

optimized to generate Fibre Channel reference clock

frequencies and is a member of the HiPerClocksTM

family of high performance clock solutions from IDT.

Using a 26.5625MHz 18pF parallel resonant crystal,

the following frequencies can be generated based on the 2

frequency select pins (F_SEL[1:0]): 212.5MHz, 187.5MHz,

159.375MHz, 106.25MHz and 53.125MHz. The ICS8421002I uses

IDT’s 3rd generation low phase noise VCO technology and can

achieve 1ps or lower typical rms phase jitter, easily meeting Fibre

Channel jitter requirements. The ICS8421002I is packaged in a

small 20-pin TSSOP package.

FEATURES

Two HSTL outputs (VOHmax = 1.5V)

Selectable crystal oscillator interface

or LVCMOS/LVTTL single-ended input

Supports the following output frequencies: 212.5MHz,

187.5MHz, 159.375MHz, 106.25MHz, 53.125MHz

VCO range: 560MHz - 680MHz

RMS phase jitter @ 212.5MHz, using a 26.5625MHz crystal

(637kHz - 10MHz): 0.59ps (typical)

Power supply modes:

Core/Output

3.3V/1.8V

2.5V/1.8V

-40°C to 85°C ambient operating temperature

Available in both standard (RoHS 5) an lead-free (RoHS 6)

packages

HiPerClockS

ICS

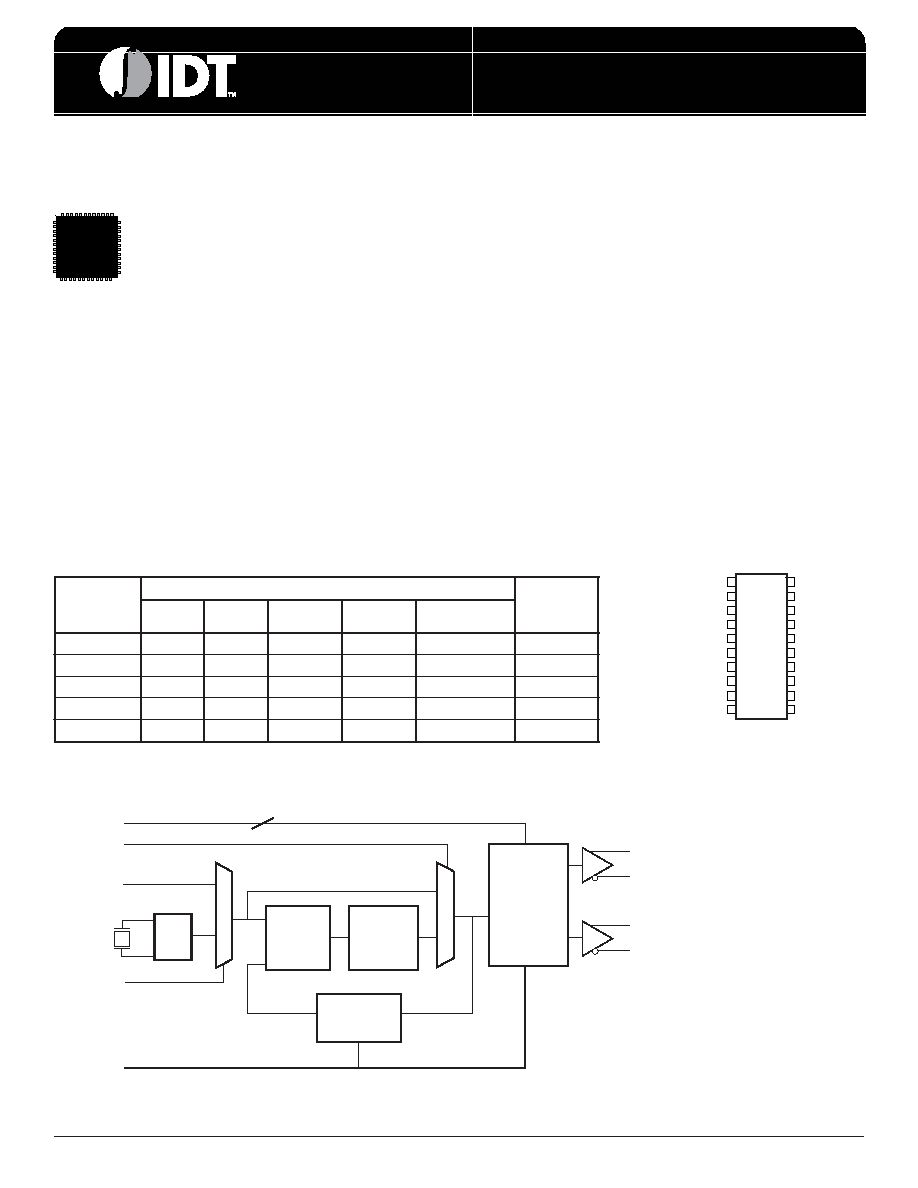

1

0

1

0

Phase

Detector

VCO

M = 24 (fixed)

F_SEL[1:0]

0 0

÷3 (default)

0 1

÷4

1 0

÷6

1 1

÷12

2

OSC

BLOCK DIAGRAM

t

u

p

n

I

y

c

n

e

u

q

e

r

F

)

z

H

M

(

s

t

u

p

n

I

t

u

p

t

u

O

y

c

n

e

u

q

e

r

F

)

z

H

M

(

1

L

E

S

_

F0

L

E

S

_

F

r

e

d

i

v

i

D

M

e

u

l

a

V

r

e

d

i

v

i

D

N

e

u

l

a

V

N

/

M

e

u

l

a

V

r

e

d

i

v

i

D

5

2

6

5

.

6

20

0

4

23

8

5

.

2

1

2

5

2

6

5

.

6

20

1

4

24

6

5

7

3

.

9

5

1

5

2

6

5

.

6

21

0

4

26

4

5

2

.

6

0

1

5

2

6

5

.

6

21

1

4

22

12

5

2

1

.

3

5

7

3

4

.

3

20

0

4

23

8

5

.

7

8

1

FREQUENCY SELECT FUNCTION TABLE

F_SEL[1:0]

nPLL_SEL

REF_CLK

XTAL_IN

XTAL_OUT

nXTAL_SEL

MR

Q0

nQ0

Q1

nQ1

Pulldown

26.5625MHz

Pulldown

ICS8421002I

20-Lead TSSOP

6.5mm x 4.4mm x 0.92mm

package body

G Package

Top View

nc

VDDO

Q0

nQ0

MR

nPLL_SEL

nc

VDDA

F_SEL0

VDD

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

VDDO

Q1

nQ1

GND

VDD

nXTAL_SEL

REF_CLK

XTAL_IN

XTAL_OUT

F_SEL1

PIN ASSIGNMENT

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ICS8422002AGILF

IC SYNTHESIZER LVHSTL 20-TSSOP

ICS8427DY-02LF

IC SYNTHESIZER 500MHZ 32-LQFP

ICS843001AG-123LF

IC SYNTHESIZER LVPECL 8-TSSOP

ICS843001AG-21LFT

IC SYNTHESIZER LVPECL 24-TSSOP

ICS843001AGI-22LFT

IC SYNTHESIZER LVPECL 24-TSSOP

ICS843001AKI-40LF

IC SYNTHESIZER LVPECL 16-VFQFPN

ICS843002AGI-01LF

IC SYNTHESIZER LVPECL 20-TSSOP

ICS843002AKI-41LF

IC SYNTHESIZER LVPECL 32-VFQFPN

相关代理商/技术参数

ICS8421002AGILFT

功能描述:IC FREQ SYNTHESIZER 20-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT

ICS8421002AGIT

制造商:ICS 制造商全称:ICS 功能描述:FEMTOCLOCKS⑩ CRYSTAL-TO-HSTL FREQUENCY SYNTHESIZER

ICS8421002AI

制造商:ICS 制造商全称:ICS 功能描述:FEMTOCLOCKS⑩ CRYSTAL-TO-HSTL FREQUENCY SYNTHESIZER

ICS8421002I

制造商:ICS 制造商全称:ICS 功能描述:FEMTOCLOCKS⑩ CRYSTAL-TO-HSTL FREQUENCY SYNTHESIZER

ICS8421002I-01

制造商:ICS 制造商全称:ICS 功能描述:FEMTOCLOCKS⑩ CRYSTAL-TO-HSTL FREQUENCY SYNTHESIZER

ICS8421004AGI

制造商:ICS 制造商全称:ICS 功能描述:FEMTOCLOCKS? CRYSTAL-TO-HSTL FREQUENCY SYNTHESIZER

ICS8421004AGI-01

制造商:ICS 制造商全称:ICS 功能描述:FEMTOCLOCKS⑩ CRYSTAL-TO-HSTL FREQUENCY SYNTHESIZER

ICS8421004AGI-01T

制造商:ICS 制造商全称:ICS 功能描述:FEMTOCLOCKS⑩ CRYSTAL-TO-HSTL FREQUENCY SYNTHESIZER